Publié le 14 février 2026 08:05:00. Des chercheurs de l’Institut des sciences de Tokyo ont mis au point une puce radar miniaturisée qui pourrait révolutionner les communications au-delà de la 5G et de la 6G, en permettant une détection d’objets et une transmission de données plus précises et plus efficaces.

- La puce, d’une superficie de seulement 0,24 mm2, consomme une puissance de seulement 9,8 mW.

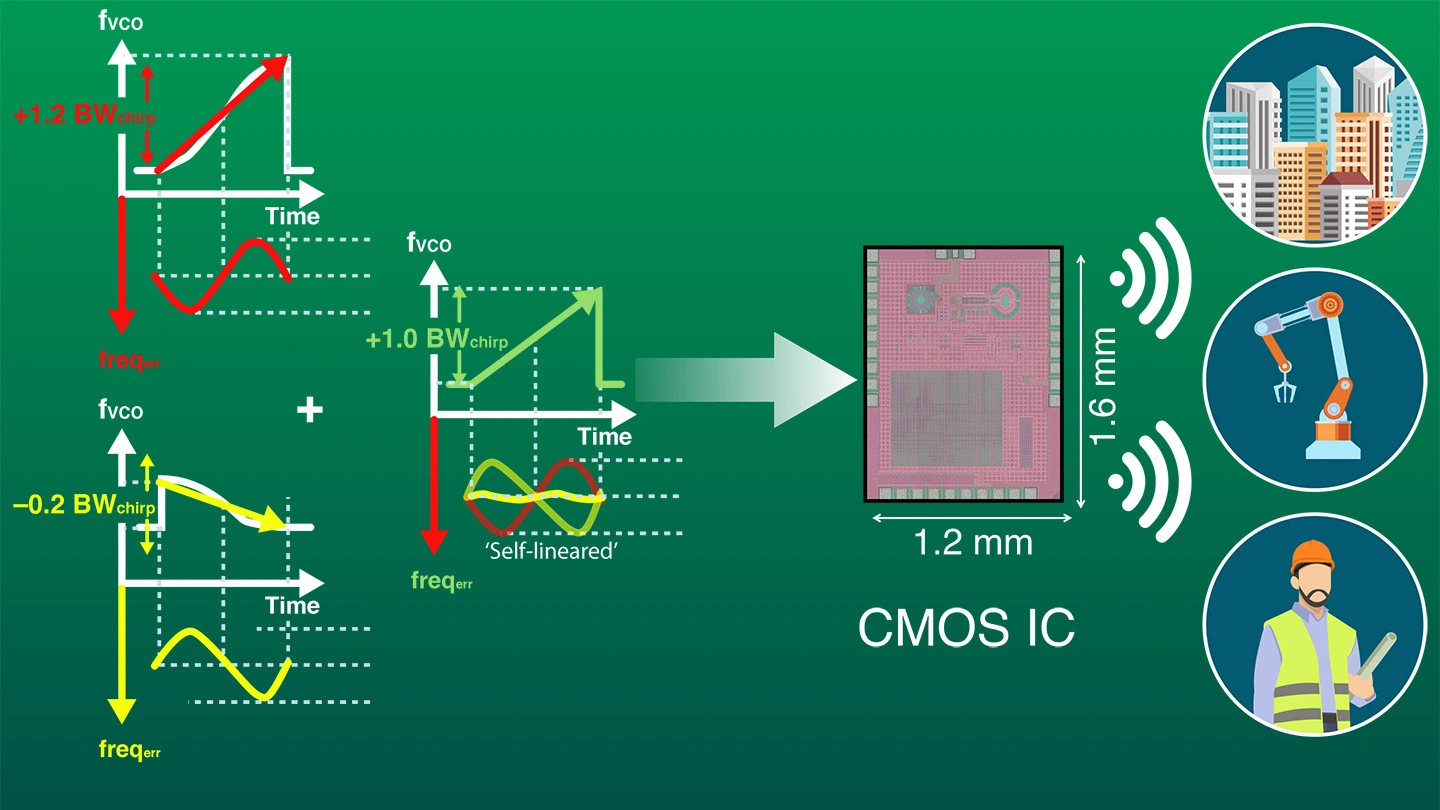

- Elle génère des signaux radar à haute vitesse et très linéaires grâce à une technique d’auto-linéarisation intégrée directement dans le matériel.

- Cette innovation devrait faciliter le développement d’applications telles que les villes intelligentes et l’Internet des objets industriel.

Une équipe de recherche dirigée par le professeur Kenichi Okada du département de génie électrique et électronique de l’Institut des sciences de Tokyo a franchi une étape importante dans le domaine de la détection et de la communication intégrées (ISAC). Cette technologie, qui combine la transmission de données sans fil avec la détection environnementale de type radar, est considérée comme une voie prometteuse pour les futures générations de réseaux mobiles, au-delà de la 5G et de la 6G. Le déploiement de l’ISAC dans la nouvelle bande de fréquences 3 (de 7,125 à 24,25 GHz) devrait ouvrir la voie à de nombreuses applications innovantes.

L’une des principales difficultés dans le développement de ces systèmes réside dans la nécessité de mesurer avec précision la distance et le mouvement des objets. Le radar à ondes continues modulées en fréquence (FMCW) est une technique couramment utilisée à cet effet. Il repose sur l’émission de signaux dont la fréquence varie de manière linéaire dans le temps, appelés « chirps », et sur l’analyse de la différence entre les ondes émises et réfléchies. La performance de ce radar dépend crucialement de la capacité à générer des signaux chirp à la fois rapides et linéaires.

La puce développée par l’équipe du professeur Okada utilise une architecture de synthétiseur de type III et fonctionne à une fréquence de 9,7 GHz. Son circuit central occupe une surface minuscule de 0,24 mm2 et consomme environ 9,8 mW, ce qui la rend idéale pour une intégration dans les appareils de périphérie (edge) et les objets connectés de l’Internet des objets (IoT). Les résultats de cette recherche seront présentés à la Conférence internationale sur les circuits à semi-conducteurs de l’IEEE 2026 (ISSCC), qui se tiendra à San Francisco, aux États-Unis, du 15 au 19 février 2026.

« Nous avons proposé une nouvelle architecture de circuit qui génère des signaux chirp, répondant à la fois aux exigences de taux de chirp élevé pour la détection de cibles en mouvement rapide, à la large bande passante nécessaire pour la télémétrie haute résolution et à la haute linéarité requise pour une mesure de haute précision dans le radar FMCW, en auto-compensant la non-linéarité de l’oscillateur contrôlé en tension (VCO) dans le circuit », explique le professeur Okada.

Les générateurs de signaux FMCW traditionnels utilisent souvent la prédistorsion numérique (DPD) pour corriger la non-linéarité de l’oscillateur. Cette technique consiste à appliquer une réponse inverse au signal d’entrée. L’équipe de Tokyo a opté pour une approche différente, intégrant directement la fonction de linéarisation dans le matériel de l’oscillateur. Cette architecture comprend un tracker de rampe qui génère le chirp tout en réduisant l’erreur de gain, et un bloc d’étalonnage de non-linéarité VCO qui compense la distorsion résiduelle. Les chercheurs ont ainsi réussi à réduire la surcharge numérique et à maintenir un fonctionnement stable, même à des taux de chirp très élevés.

Un prototype de puce fabriqué à l’aide d’un processus CMOS de 65 nanomètres a démontré la capacité de générer des signaux chirp à 9,7 GHz avec une bande passante de balayage de 1 GHz. « Il atteint une durée de chirp de 0,57 μs, un retracement de 40 ns et un taux de chirp de 1 562,8 MHz/μs, offrant une bande passante de 1 GHz avec une erreur FM de 0,094 % rms », précise le professeur Okada.

Cette avancée technologique représente une étape décisive vers le déploiement pratique de l’ISAC dans une large gamme d’appareils de pointe et d’objets connectés, ouvrant la voie à une société 6G parfaitement interconnectée.

Ces résultats de recherche ont été obtenus grâce à un financement de l’Institut national des technologies de l’information et des communications (NICT) du Japon (recherche commandée n° JPJ012368C00801).

- Auteurs :

- Daxu Zhang, Yuncheng Zhang, Zezheng Liu, Yuang Xiong, Michele Rossoni, Wenqian Wang, Ashbir Aviat Fadila, Duo Li, Minzhe Tang, Dongfan Xu, Carrel de Gomez, Dingxin Xu, Kazuaki Kunihiro, Hiroyuki Sakai et Kenichi Okada*

*Auteur correspondant - Titre:

- Un générateur Chirp FMCW auto-linéarisé basé sur VCO de 9,7 GHz atteignant une pente de 1,56 GHz/μs et une durée de 0,57 μs avec une erreur de fréquence de 0,094 % efficace.

<p>

<dt class="c-definitionList__term">Affiliations :</dt>

<dd class="c-definitionList__description">Département de génie électrique et électronique, Institute of Science Tokyo, Japon</dd>